Authors: Jameson Thies, Amirhossein Alimohammad

Publication: IEEE Transactions on Neural Systems and Rehabilitation Engineering

Date: July 16, 2019

DOI: 10.1109/TNSRE.2019.2929081

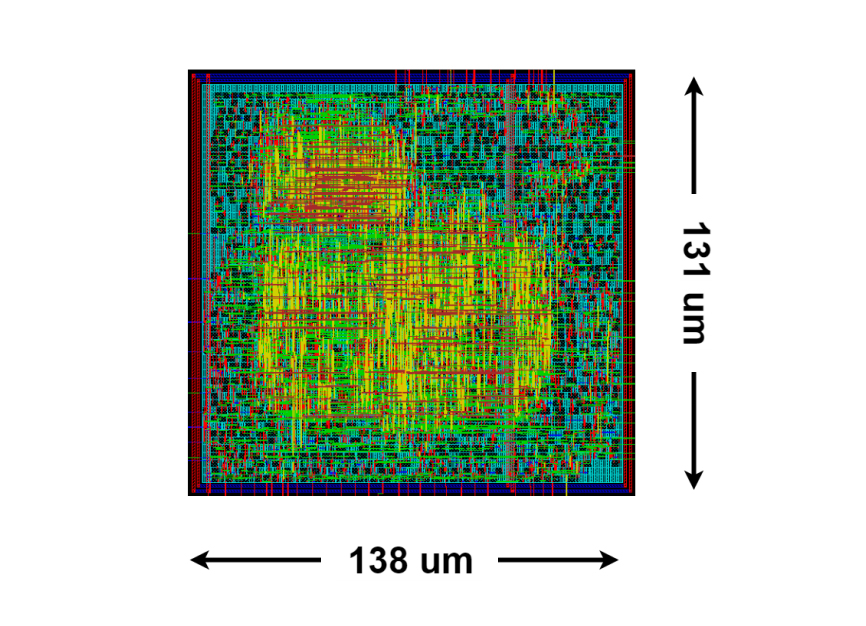

Implantable microsystems which collect and transmit neural data are becoming very useful entities in the field of neuroscience. Limited by high data rates, on-chip compression is often required to transmit the recorded data without causing power dissipation at levels that would damage sensitive brain tissue. This article presents a data compression system designed for brain computer interfaces (BCIs) based on undercomplete autoencoders. To the best of our knowledge, the proposed system is the first to achieve an average spike reconstruction quality of 14 dB signal-to-noise-and-distortion ratio (SNDR) at a 32× compression ratio (CR), 18 dB SNDR at a 16× CR, 22 dB SNDR at an 8× CR, and 35 dB SNDR at a 4× CR of neural spikes. The spike detection and autoencoder-based compression modules are designed and implemented in a standard 45-nm CMOS process. The post synthesis simulation results report that the compression module consumes between 1.4 μW and 222.5 μW of power per channel and takes between 0.018 mm2 and 0.082 mm2 of silicon area, depending on the desired CR and number of channels.